Links

Abstract

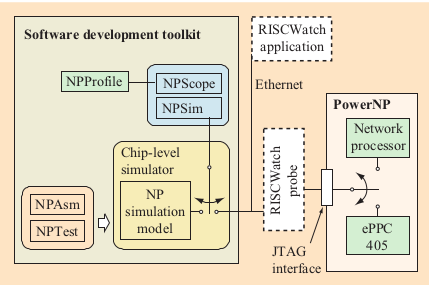

Deep packet processing is migrating to the edges of service provider networks to simplify and speed up core functions. On the other hand, the cores of such networks are migrating to the switching of high-speed traffic aggregates, e.g., using switching with dense wavelength division multiplexing (DWDM). As a result, more services will need to be performed at the edges, both on behalf of the core and end users. Associated network equipment will therefore require high flexibility to support evolving high-level services as well as extraordinary performance to deal with the high packet rates. Whereas in the past network equipment were based either on general-purpose processors (GPPs) or application-specific integrated circuits (ASICs), favoring flexibility over speed or vice versa, the network processor approach achieves both flexibility and performance. The key advantage of network processors is that hardware-level performance is complemented by flexible software architecture. In this paper, we describe the IBM PowerNP&tm; NP4GS3 network processor and how it addresses these issues. Its hardware and software design characteristics and its comprehensive base operating software of this network processor make it well suited for a wide range of networking applications.

BibTeX (Download)

@article{Allen2003PowerNP,

title = {IBM PowerNP Network Processor: Hardware Software and Applications},

author = {James Allen and Brian Bass and Claude Basso and Rick Boivie and Jean Calvignac and Gordon Davis and Laurent Freléchoux and Marco Heddes and Andreas Herkersdorf and Andreas Kind and Joe Logan and Mohammad Peyravian and Mark Rinaldi and Ravi Sabhikhi and Michael Siegel and Marcel Waldvogel},

url = {https://netfuture.ch/wp-content/uploads/2003/allen03powernp.pdf},

year = {2003},

date = {2003-01-01},

urldate = {1000-01-01},

journal = {IBM Journal of Research and Development},

volume = {47},

number = {2/3},

pages = {177-194},

abstract = {Deep packet processing is migrating to the edges of service provider networks to simplify and speed up core functions. On the other hand, the cores of such networks are migrating to the switching of high-speed traffic aggregates, e.g., using switching with dense wavelength division multiplexing (DWDM). As a result, more services will need to be performed at the edges, both on behalf of the core and end users. Associated network equipment will therefore require high flexibility to support evolving high-level services as well as extraordinary performance to deal with the high packet rates. Whereas in the past network equipment were based either on general-purpose processors (GPPs) or application-specific integrated circuits (ASICs), favoring flexibility over speed or vice versa, the network processor approach achieves both flexibility and performance. The key advantage of network processors is that hardware-level performance is complemented by flexible software architecture. In this paper, we describe the IBM PowerNP&tm; NP4GS3 network processor and how it addresses these issues. Its hardware and software design characteristics and its comprehensive base operating software of this network processor make it well suited for a wide range of networking applications.},

keywords = {Fast Routers, Network Processors, Quality of Service},

pubstate = {published},

tppubtype = {article}

}