[simple_series title=”CRC Tutorial”]

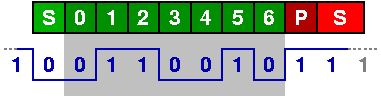

One of the oldest forms of computer-based error checking is the use of parity bits, predominantly used in asynchronous serial line communications, such as the RS-232 connection used between computer and modem. For RS-232 and some other serial asynchronous protocols, each symbol (cf. upper half of the image) is preceded by a start bit (S) indicating the beginning of symbol, a series of data bits (0-6, least-significant bit first; i.e., the bit sequence shown is actually the seven-digit binary (base-2) number <01001102), optional parity (P) to provide limited transmission verification, and 1-2 stop bits (S) concluding the symbol. The value of the start bit (cf. bottom half of the image) is the opposite of the “idle” bit which is visible on the line if no symbol is currently transmitted. The transition from “idle” to “start” raises the attention of the receiver on the incoming symbol. The stop bit(s) have the same value as the “idle” signal. Their purpose is to guarantee a minimum idle period, such that the next start bit is guaranteed to have a recognizable 0-1 transition. To further facilitate this recognition, 1.5 start bits were popular in earlier times, as half bit-lengths could not occur within a symbol and therefore it must be a stop bit. The start and stop bits are also

referred to as framing.