Links

Abstract

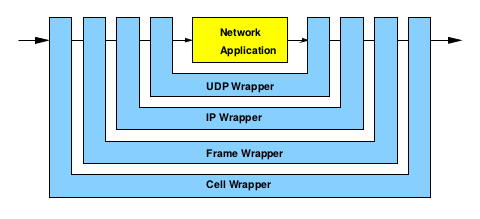

A library of layered protocol wrappers has been developed that process Internet packets in reconfigurable hardware. These wrappers can be used with a reprogrammable network platform called the Field Programmable Port Extender (FPX) to rapidly prototype hardware circuits for processing Internet packets. We present a framework to streamline and simplify the development of networking applications that process ATM cells, AAL5 frames, Internet Protocol (IP) packets and UDP datagrams directly in hardware.

BibTeX (Download)

@inproceedings{Braun2001Layered,

title = {Layered Protocol Wrappers for Internet Packet Processing in Reconfigurable Hardware},

author = {Florian Braun and John Lockwood and Marcel Waldvogel},

url = {https://netfuture.ch/wp-content/uploads/2001/braun01layered.pdf},

year = {2001},

date = {2001-08-01},

urldate = {1000-01-01},

booktitle = {Proceedings of IEEE Hot Interconnects 9},

address = {Stanford, CA, USA},

abstract = { A library of layered protocol wrappers has been developed that process Internet packets in reconfigurable hardware. These wrappers can be used with a reprogrammable network platform called the Field Programmable Port Extender (FPX) to rapidly prototype hardware circuits for processing Internet packets. We present a framework to streamline and simplify the development of networking applications that process ATM cells, AAL5 frames, Internet Protocol (IP) packets and UDP datagrams directly in hardware.},

keywords = {Fast Routers, FPGA},

pubstate = {published},

tppubtype = {inproceedings}

}