# WASHINGTON UNIVERSITY

# SEVER INSTITUTE OF TECHNOLOGY

# INTEGRATED HARDWARE/SOFTWARE DESIGN OF A HIGH PERFORMANCE NETWORK INTERFACE

by

Zubin Dittia

Prepared under the direction of Professor Gurudatta M. Parulkar

A dissertation presented to the Sever Institute of

Washington University in partial fulfillment

of the requirements for the degree of

DOCTOR OF SCIENCE

May 2001

Saint Louis, Missouri

### WASHINGTON UNIVERSITY

### SEVER INSTITUTE OF TECHNOLOGY

## ABSTRACT

## INTEGRATED HARDWARE/SOFTWARE DESIGN OF A HIGH PERFORMANCE NETWORK INTERFACE

by Zubin Dittia

ADVISOR: Professor Gurudatta M. Parulkar

May, 2001

Saint Louis, Missouri

This thesis describes the design and implementation of a high performance network interface chip called the APIC (ATM Port Interconnect Controller). It also describes architectural enhancements to operating system (OS) software that are necessary to exploit some of the novel features that have been integrated into this chip.

High-performance network interface design has received significant interest from the research community in recent years because traditional design methodologies have not been successful in translating high network bandwidths and low network latencies to improved performance for applications. This can be attributed to several factors: in the past network interfaces have been designed without careful consideration of the operating system software environment in which they get used; main memory bandwidths have not scaled at the same rate as network bandwidths; and network interfaces and protocols have not been designed to support quality of service for applications. These are the problems addressed by this thesis, the objective being to develop new mechanisms which can result in significant improvements in application performance. In addition to incorporating these innovative features, the APIC design borrows proven and useful ideas from a number of commercial and research prototypes.

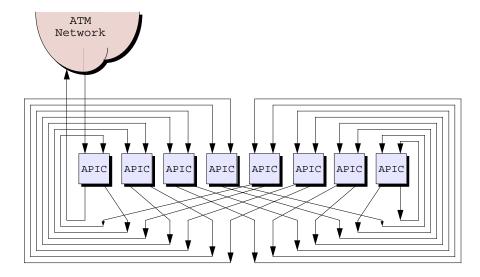

One of the ways in which the APIC addresses the memory bottleneck alluded to above is to function in a desk-area environment where different memories can be used to spread the load. The idea here is to dedicate one APIC chip and one memory bank to each high-bandwidth device in the system, thereby shedding the load from a host system's main memory. Several such APIC-memory-device combinations can be daisy chained to form a desk-area network with high bandwidth and low latency characteristics.

There are several well-known operating system overheads associated with in-kernel implementations of network interface device drivers. These include context switch latency, system call overhead, and interrupt overhead. It is possible to remove a number of these inefficiencies and allow for increased performance for end applications if the data path of the device driver can be implemented as a library in user-space. While this idea has been proposed in the recent past, the APIC introduces two new mechanisms, Protected DMA and Protected I/O, which together provide for an efficient method for the implementation of user-space drivers.

Another problem which plagues high-speed network adapters is called receive livelock; this term is used to describe the situation in which, under heavy load, an operating system servicing a device might end up spending all its time in the interrupt service routine, and no useful work gets done. The APIC introduces a novel concept called Interrupt Demultiplexing, which taken alone can alleviate the effects of interrupt livelock, but in conjunction with user-space drivers can solve the problem entirely.

Network interfaces, except for ATM interfaces, have traditionally not provided special mechanisms for supporting quality-of-service (QoS) guarantees. Even ATM interfaces have traditionally supported QoS only to a limited extent. By providing pacing support independently for large numbers of connections, the APIC is able to efficiently and reliably support QoS guarantees simultaneously for large numbers of multimedia streams. This can be especially useful in the context of large multimedia-on-demand servers. This feature was made possible through a novel pacer design which uses a hardware d-heap data structure.

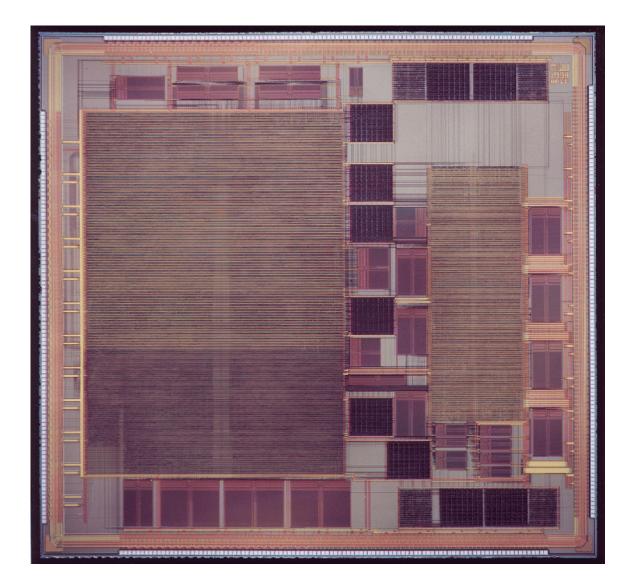

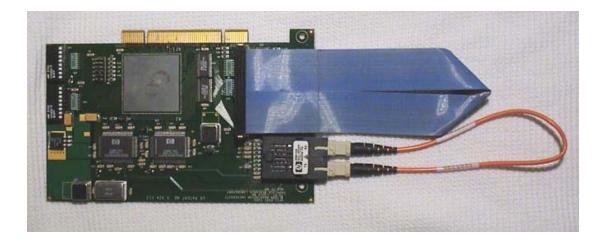

The APIC has been successfully implemented in 0.35 micron technology, and is currently in use in several projects both at Washington University and elsewhere, as part of the NSF-sponsored gigabit kits project.

to my parents

# Contents

| Та | bles      | viii                                                      |

|----|-----------|-----------------------------------------------------------|

| Fi | gures     | ix                                                        |

| Ac | cknowledg | gements xii                                               |

| 1  | Introdu   | ction1                                                    |

|    | 1.1       | Goals                                                     |

|    | 1.2       | Features of the APIC Chip                                 |

|    | 1.3       | Contributions                                             |

|    | 1.4       | Outline                                                   |

| 2  | Backgro   | ound and Motivation                                       |

|    | 2.1       | DMA Subsystems 7                                          |

|    |           | 2.1.1 Why is the DMA Subsystem so important?              |

|    |           | 2.1.2 NIC design choices that affect the DMA Subsystem 11 |

|    | 2.2       | Architectural Impact on Latency 13                        |

|    |           | 2.2.1 Impact of interrupts on latency                     |

|    | 2.3       | Receive Livelock                                          |

|    | 2.4       | QoS Support in Network Interfaces                         |

|   | 2.5     | User-space Protocol Implementations              | 18 |

|---|---------|--------------------------------------------------|----|

| 3 | Related | Work                                             | 23 |

|   | 3.1     | Related work in network interface design         | 23 |

|   | 3.2     | Network interfaces supporting user-space control | 27 |

|   | 3.3     | Desk-Area Networks                               | 30 |

|   | 3.4     | Reducing Interrupt Overhead                      | 30 |

|   | 3.5     | Receive Livelock Elimination                     | 31 |

|   | 3.6     | QoS support for network interfaces               | 31 |

| 4 | Contrib | utions                                           | 34 |

|   | 4.1     | Problem Statement                                | 34 |

|   | 4.2     | Overview of Solutions                            | 35 |

| 5 | Archite | cture Overview                                   | 39 |

|   | 5.1     | APIC as a Network Interface Device               | 39 |

|   | 5.2     | APIC-based DANs                                  | 40 |

|   | 5.3     | Ports and Connections                            | 43 |

|   |         | 5.3.1 The ATM Ports                              | 43 |

|   |         | 5.3.2 The Bus Port                               | 43 |

|   |         | 5.3.3 Virtual Connections (VCs)                  | 44 |

|   | 5.4     | Basic Operation                                  | 44 |

|   |         | 5.4.1 Segmentation and Reassembly                | 45 |

|   |         | 5.4.2 Packets and Frames                         | 45 |

|   |         | 5.4.3 Cut-through Behavior                       | 45 |

|   |         | 5.4.4 Channels and Connections (VCs)             | 47 |

|   | 5.5     | Summary of Features                              | 47 |

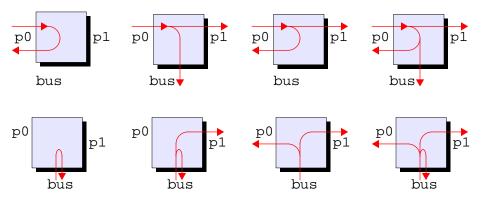

|   |         | 5.5.1 Multipoint and Loopback                    | 47 |

|   |         | 5.5.2 AAL-0                                      | 49 |

|   |         | 5.5.3 AAL-5                                      | 50 |

|   |         | 5.5.4   | Traffic Types                                          | 50 |

|---|---------|---------|--------------------------------------------------------|----|

|   |         | 5.5.5   | Batching                                               | 52 |

|   |         | 5.5.6   | Remote Control                                         | 53 |

|   | 5.6     | User-S  | Space Control                                          | 55 |

|   |         | 5.6.1   | Protected I/O                                          | 55 |

|   | 5.7     | DMA     | Modes                                                  | 60 |

|   |         | 5.7.1   | Simple DMA                                             | 62 |

|   |         | 5.7.2   | Pool DMA                                               | 64 |

|   |         | 5.7.3   | Protected DMA                                          | 65 |

|   |         | 5.7.4   | Packet Splitting                                       | 69 |

|   | 5.8     | Interru | ıpt Mechanisms                                         | 72 |

|   |         | 5.8.1   | Interrupt Demultiplexing                               | 72 |

|   |         | 5.8.2   | Orchestrated Interrupts                                | 76 |

|   |         | 5.8.3   | Notification Lists                                     | 77 |

|   | 5.9     | Misce   | llaneous Features                                      | 77 |

|   |         | 5.9.1   | TCP Checksum Assist                                    | 77 |

|   |         | 5.9.2   | Flow Control                                           | 78 |

|   |         | 5.9.3   | Cache Coherent Bus Transfers                           | 79 |

| 6 | Interna | l Desig | n of the APIC Chip                                     | 81 |

|   | 6.1     | Clock   | Regimes                                                | 82 |

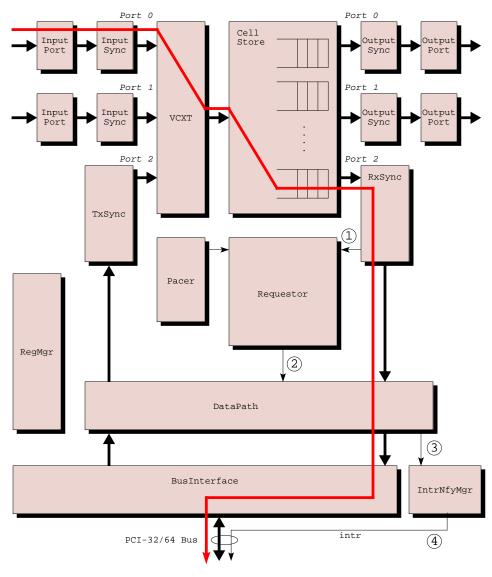

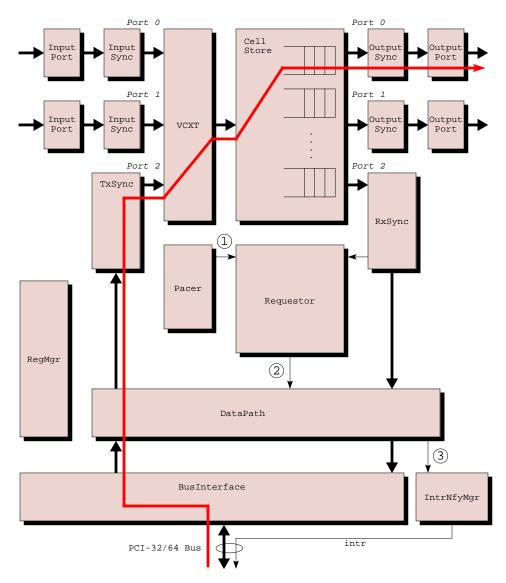

|   | 6.2     | Modu    | le Functions and Paths Taken by Cells Through the Chip | 83 |

|   |         | 6.2.1   | Synchronization Modules                                | 83 |

|   |         | 6.2.2   | Input and Output Ports                                 | 84 |

|   |         | 6.2.3   | BusInterface                                           | 84 |

|   |         | 6.2.4   | RegisterManager                                        | 84 |

|   |         | 6.2.5   | VCXT                                                   |    |

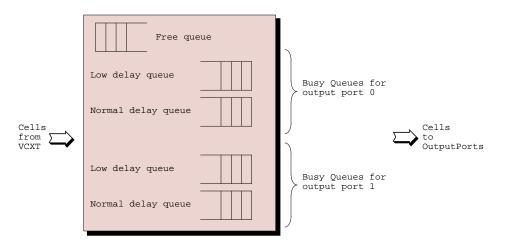

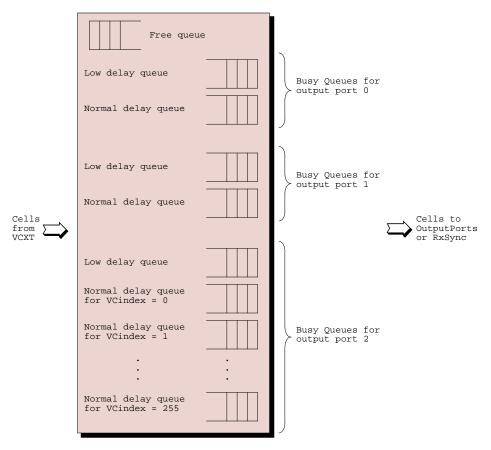

|   |         | 6.2.6   | CellStore                                              | 88 |

|   |         | 6.2.7   | RxSync                                                 | 92 |

|   |         | 6.2.8   | Requestor                                              | 92 |

|          | 6.2.9 DataPath                                 |     |

|----------|------------------------------------------------|-----|

|          | 6.2.10 IntrNfyMgr                              |     |

| 6.3      | Pacer Design                                   | 102 |

| 7 APIC S | oftware                                        | 105 |

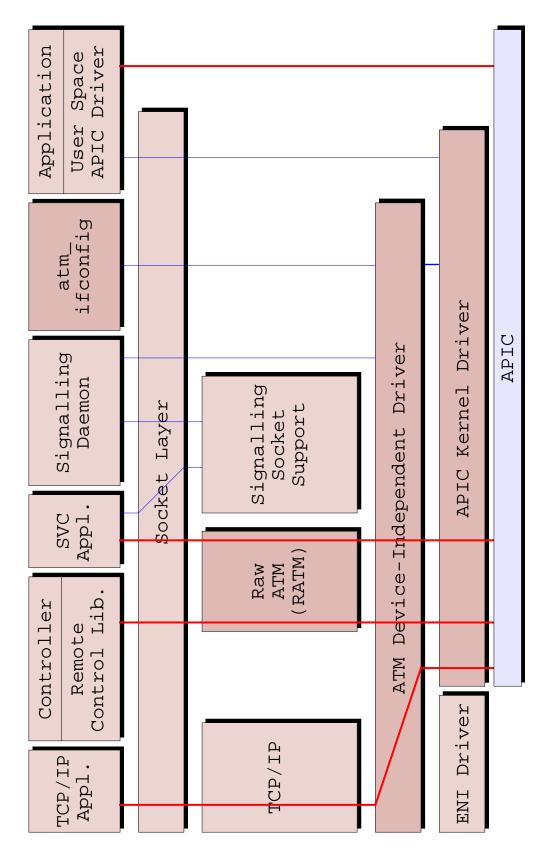

| 7.1      | Overall Software Framework                     | 105 |

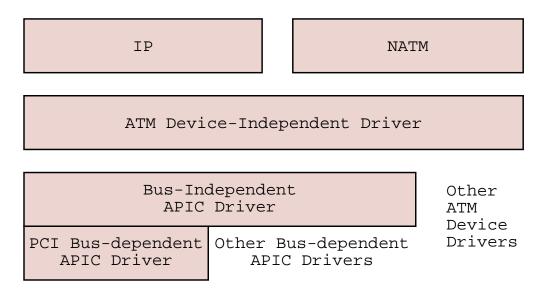

| 7.2      | Kernel Driver Structure                        | 109 |

|          | 7.2.1 Interaction with IP                      | 110 |

|          | 7.2.2 Interaction with RATM                    | 111 |

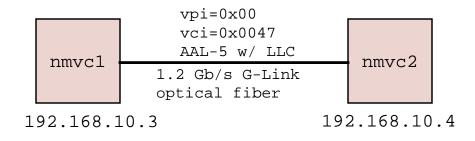

| 8 Experi | mental Results                                 | 113 |

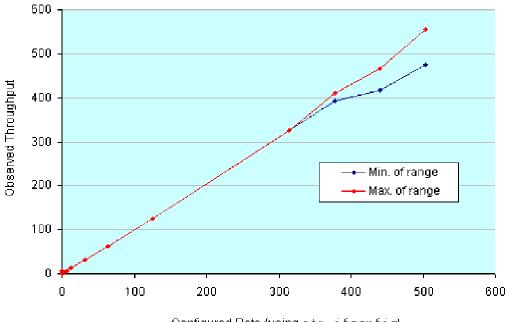

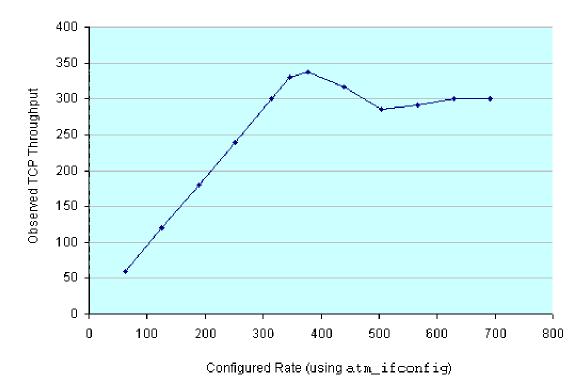

| 8.1      | Best-effort TCP Throughput                     | 114 |

| 8.2      | Pacing Test for UDP Traffic                    |     |

| 8.3      | Pacing Test for TCP Traffic                    | 116 |

| 8.4      | End-to-end Delay and Driver Performance        |     |

| 8.5      | Protected DMA Throughput and Delay Performance | 119 |

| 9 Conclu | sions                                          | 122 |

| 9.1      | Contributions                                  | 122 |

| 9.2      | Future Work                                    | 125 |

| 9.3      | Closing Remarks                                | 126 |

|          |                                                |     |

| Vita     |                                                |     |

# **Tables**

| 4.1 | Comparison with Other Network Interfaces                  | . 38  |

|-----|-----------------------------------------------------------|-------|

|     |                                                           |       |

| 8.1 | Performance metrics for NetBSD on PCs used in experiments | . 114 |

| 8.2 | Probe points in the protocol stack                        | . 118 |

| 8.3 | Results of Ping-Pong Test                                 | . 120 |

| 8.4 | Results of User-Space Throughput Test                     | . 120 |

# Figures

| 2.1 | Typical Host Architecture                                    | . 7  |

|-----|--------------------------------------------------------------|------|

| 2.2 | Data Touch Overhead in a Typical Protocol Stack              | . 9  |

| 2.3 | Impact of On-board Memory on Data Touches                    | . 12 |

| 2.4 | Illustration of Receive Livelock                             | . 15 |

| 2.5 | Behavior of a paced channel                                  | . 17 |

| 2.6 | Traditional versus User-space Control Model                  | . 20 |

| 2.7 | Protection concerns in the user-space control model          | . 21 |

|     |                                                              |      |

| 3.1 | Network Adapter Board (NAB) Architecture                     | . 23 |

| 3.2 | Providing protected access to registers using VM overloading | . 28 |

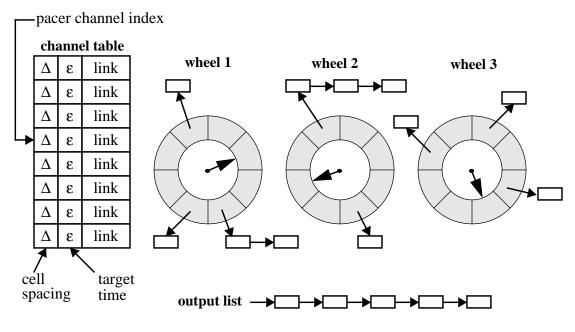

| 3.3 | Turner's Pacing Algorithm                                    | . 33 |

|     |                                                              |      |

| 5.1 | Location of an ATM NIC in a Computer System                  | . 40 |

| 5.2 | An APIC Interconnect as a Desk Area Network                  | . 41 |

| 5.3 | Perfect Shuffle Topology                                     | . 42 |

| 5.4 | Instances of Multipoint and Loopback Connections             | . 48 |

| 5.5 | An Example Multipoint Application                            | . 48 |

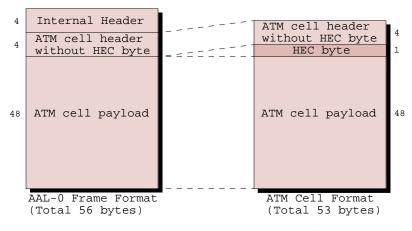

| 5.6 | AAL-0 Frames and SAR                                         | . 50 |

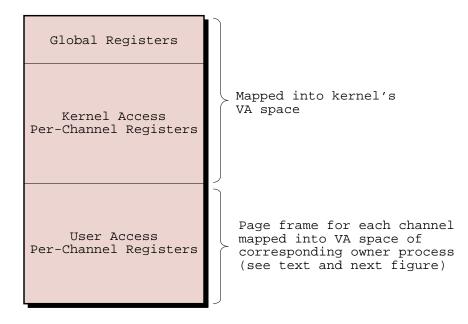

| 5.7 | Memory-Mapped I/O Address Space of the APIC                  | . 56 |

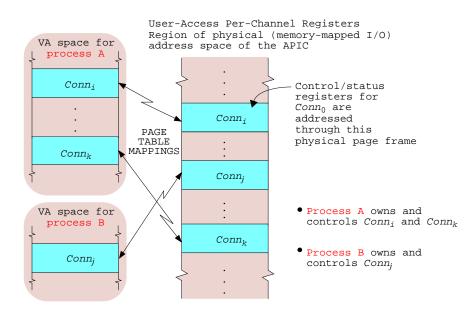

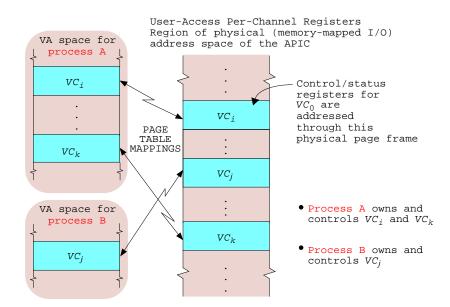

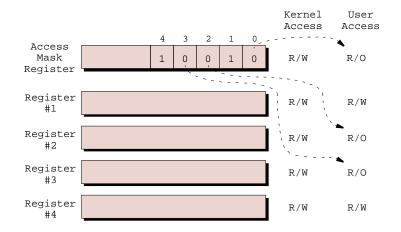

| 5.8 | Providing Protected Access to Registers using VM Overloading | . 58 |

| 5.9                                                                                                                                                                       | Fine Grain Access Control Using Protected I/O                                                                                                                                       | 59                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

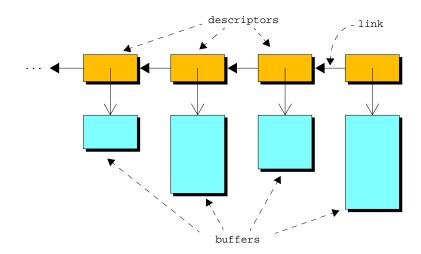

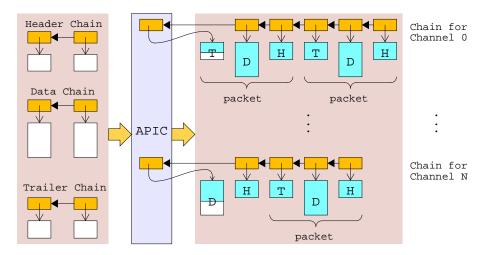

| 5.10                                                                                                                                                                      | A Descriptor Chain                                                                                                                                                                  | 60                                                                   |

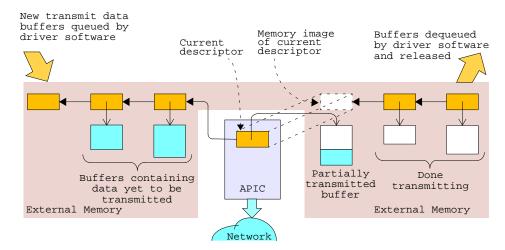

| 5.11                                                                                                                                                                      | Transmitting Data Using a Descriptor Chain                                                                                                                                          | 61                                                                   |

| 5.12                                                                                                                                                                      | FIFO Queue Model for a Transmit Descriptor Chain                                                                                                                                    | 61                                                                   |

| 5.13                                                                                                                                                                      | FIFO Queue Model for a Receive Descriptor Chain                                                                                                                                     | 62                                                                   |

| 5.14                                                                                                                                                                      | Receiving Data Using a Descriptor Chain                                                                                                                                             | 62                                                                   |

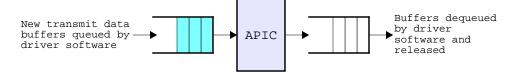

| 5.15                                                                                                                                                                      | Illustration of Simple DMA                                                                                                                                                          | 63                                                                   |

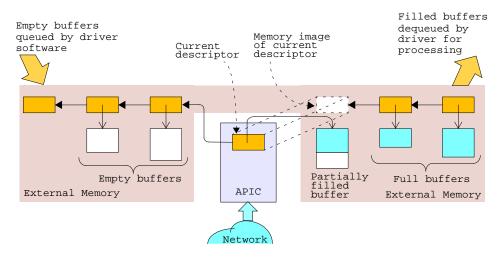

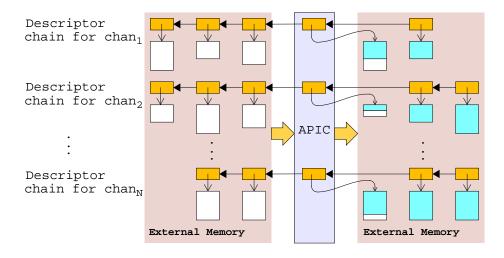

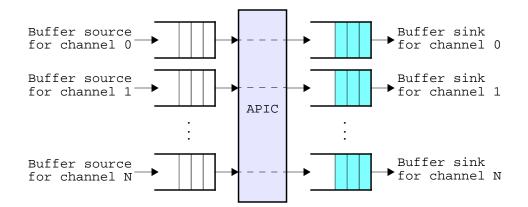

| 5.16                                                                                                                                                                      | FIFO Queue Model for Simple DMA                                                                                                                                                     | 63                                                                   |

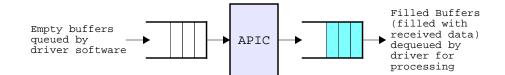

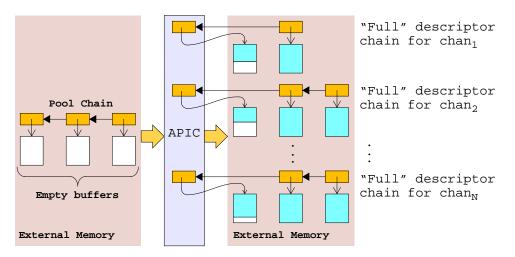

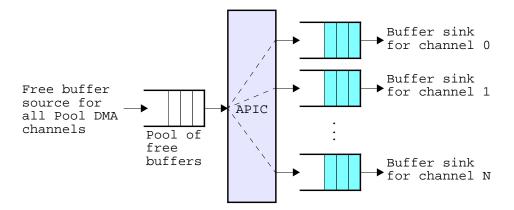

| 5.17                                                                                                                                                                      | Illustration of Pool DMA                                                                                                                                                            | 64                                                                   |

| 5.18                                                                                                                                                                      | FIFO Queue Model for Pool DMA                                                                                                                                                       | 64                                                                   |

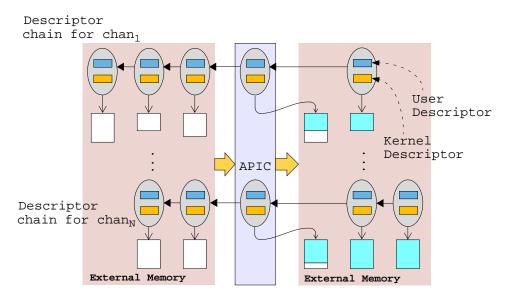

| 5.19                                                                                                                                                                      | Illustration of Protected DMA                                                                                                                                                       | 66                                                                   |

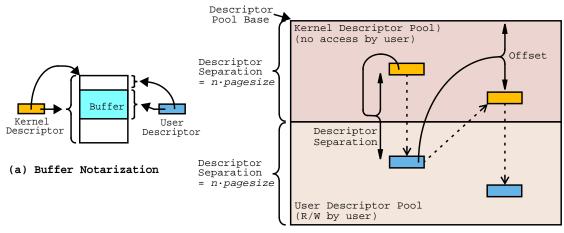

| 5.20                                                                                                                                                                      | Notarization for Protected DMA                                                                                                                                                      | 67                                                                   |

| 5.21                                                                                                                                                                      | Pool DMA with Packet Splitting                                                                                                                                                      | 69                                                                   |

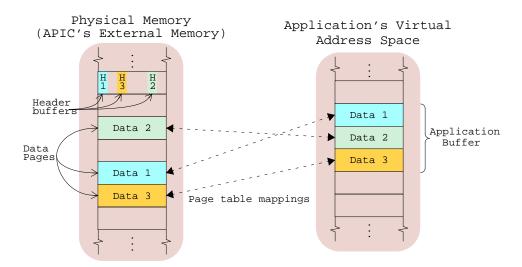

| 5.22                                                                                                                                                                      | Zero-Copy Using Packet Splitting and Page Remapping                                                                                                                                 | 70                                                                   |

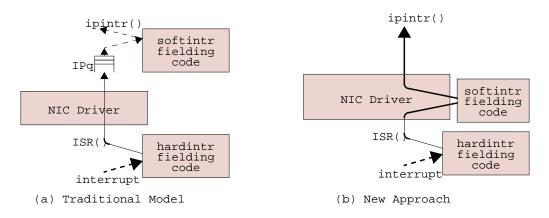

| 5.23                                                                                                                                                                      | A Different Way of Structuring a NIC Driver                                                                                                                                         | 74                                                                   |

|                                                                                                                                                                           |                                                                                                                                                                                     |                                                                      |

|                                                                                                                                                                           |                                                                                                                                                                                     |                                                                      |

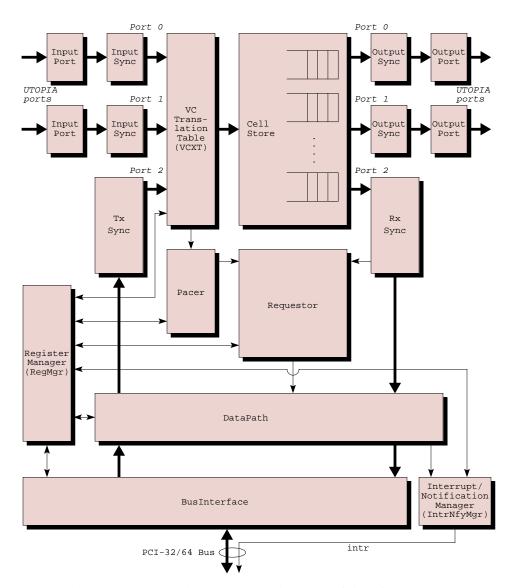

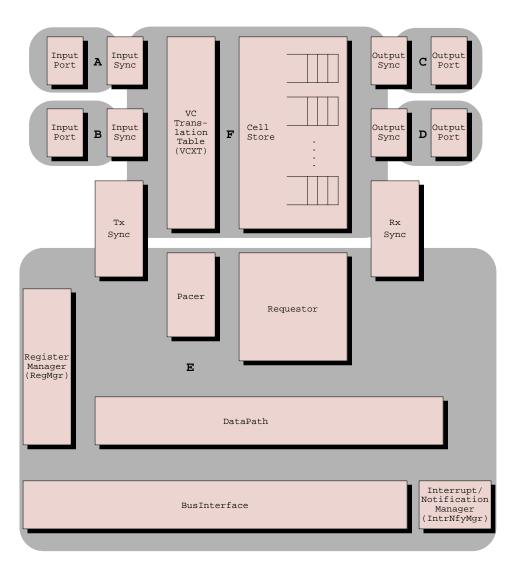

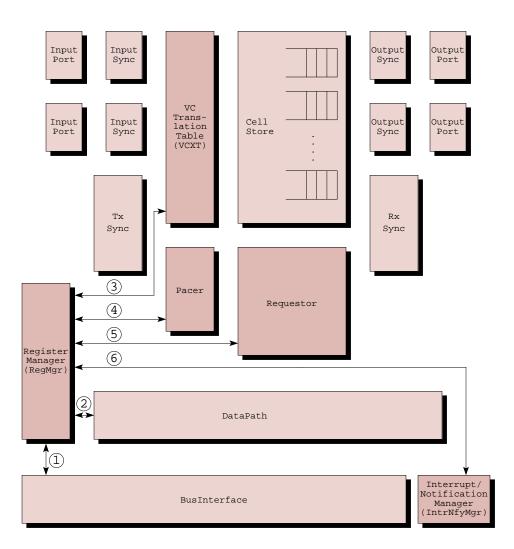

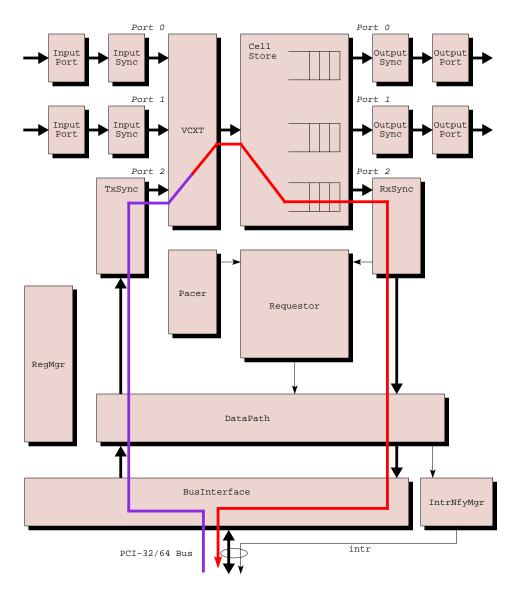

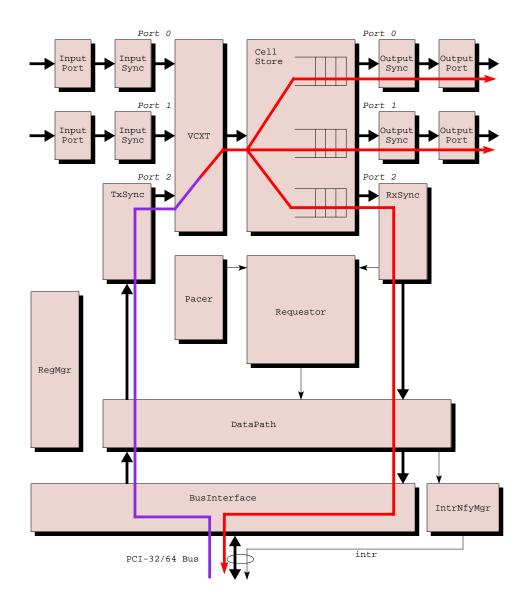

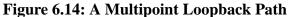

| 6.1                                                                                                                                                                       | Functional Block Diagram of APIC Internals                                                                                                                                          |                                                                      |

|                                                                                                                                                                           |                                                                                                                                                                                     | 82                                                                   |

| 6.1                                                                                                                                                                       | Functional Block Diagram of APIC Internals                                                                                                                                          | 82<br>83                                                             |

| 6.1<br>6.2                                                                                                                                                                | Functional Block Diagram of APIC Internals                                                                                                                                          | 82<br>83<br>85                                                       |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                                                             | Functional Block Diagram of APIC Internals<br>APIC Clock Regimes<br>Operation of the RegisterManager Module                                                                         | 82<br>83<br>85<br>86                                                 |

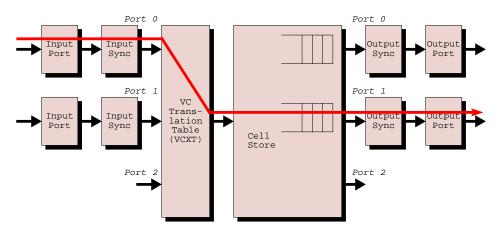

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul>                                                                                               | Functional Block Diagram of APIC Internals<br>APIC Clock Regimes<br>Operation of the RegisterManager Module<br>Transit Path Forwarding                                              | 82<br>83<br>85<br>86<br>86                                           |

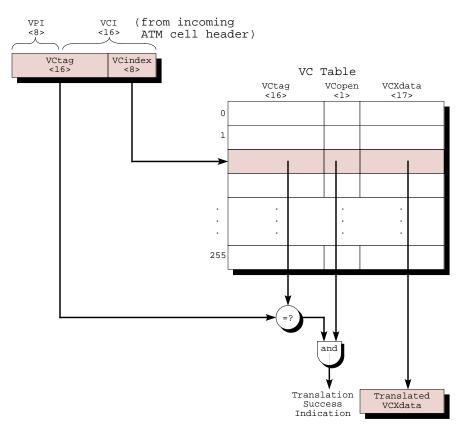

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul>                                                                                               | Functional Block Diagram of APIC Internals<br>APIC Clock Regimes<br>Operation of the RegisterManager Module<br>Transit Path Forwarding<br>VC Translation Process in the VCXT Module | 82<br>83<br>85<br>86<br>86<br>89                                     |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>                                                                                  | Functional Block Diagram of APIC Internals                                                                                                                                          | 82<br>83<br>85<br>86<br>86<br>89<br>90                               |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul>                                                                     | Functional Block Diagram of APIC Internals                                                                                                                                          | 82<br>83<br>85<br>86<br>86<br>89<br>90<br>91                         |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> </ul>                                           | Functional Block Diagram of APIC Internals                                                                                                                                          | 82<br>83<br>85<br>86<br>86<br>89<br>90<br>91<br>94                   |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> </ul>                             | Functional Block Diagram of APIC Internals                                                                                                                                          | 82<br>83<br>85<br>86<br>86<br>89<br>90<br>91<br>94<br>96             |

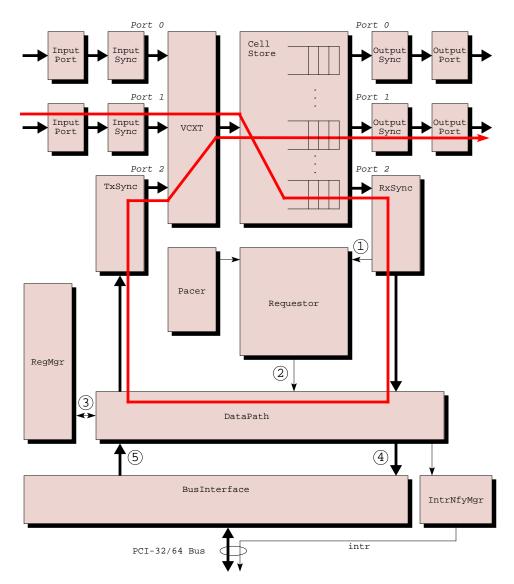

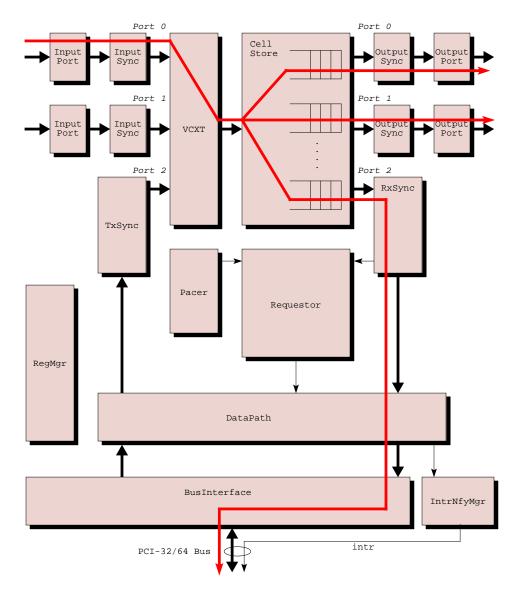

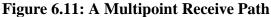

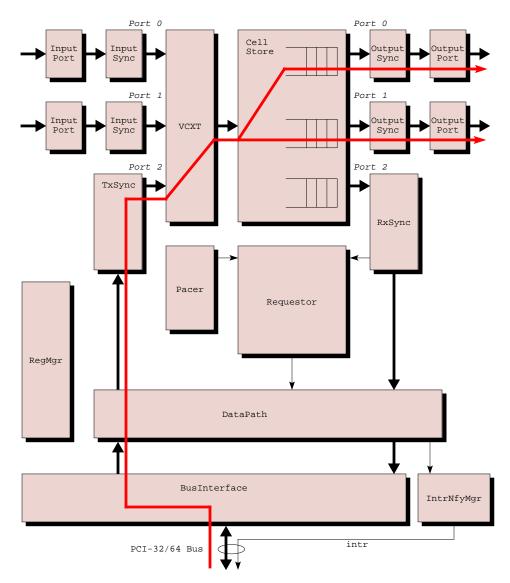

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> </ul>               | Functional Block Diagram of APIC Internals                                                                                                                                          | 82<br>83<br>85<br>86<br>86<br>89<br>90<br>91<br>94<br>96<br>98       |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> <li>6.12</li> </ul> | Functional Block Diagram of APIC Internals                                                                                                                                          | 82<br>83<br>85<br>86<br>86<br>89<br>90<br>91<br>94<br>96<br>98<br>99 |

| 6.15 | d-Heap Based Pacing                                  | 103 |

|------|------------------------------------------------------|-----|

| 7.1  | Software Framework for the APIC                      | 106 |

| 7.2  | APIC Kernel Driver Structure                         | 108 |

| 7.3  | Example Code to Illustrate RATM Access to the APIC   | 111 |

|      |                                                      |     |

| 8.1  | Experimental Setup                                   | 113 |

| 8.2  | Throughput vs. Specified Pacing Rate for UDP Traffic | 115 |

| 8.3  | Throughput vs. Specified Pacing Rate for TCP Traffic | 116 |

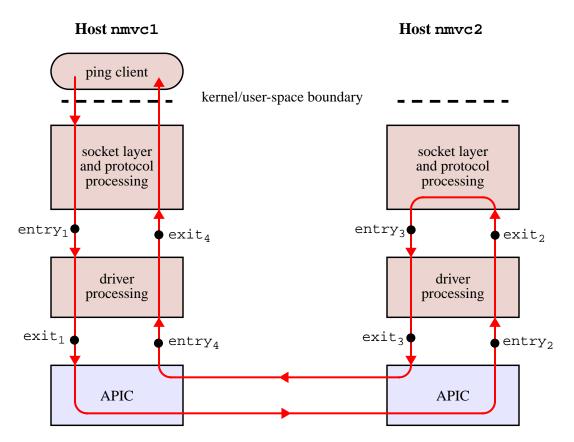

| 8.4  | Measuring APIC delay and round-trip time performance | 118 |

|      |                                                      |     |

| 9.1  | APIC Internal Layout                                 | 124 |

| 9.2  | The APIC Network Interface Card                      | 125 |

# Acknowledgements

First and foremost, I would like to thank my advisor Guru Parulkar, to whose help and encouragement I owe everything. This research would not have been possible without him, and I thank him for his patience in dealing with my sometimes difficult work habits, and for always providing the right mix of freedom, encouragement, and perspective that few advisors can provide for their students.

Second, I would like to thank Dr. Jerry Cox, who has been involved with this project from the onset, and who has made significant contributions to the design effort. He was like a second advisor to me in this undertaking. In particular, a large portion of the internal design of the APIC chip is due to him, including many of the details of implementation of the pacing algorithm described here.

I would also like to thank Rex Hill and Will Eatherton, both of whom were responsible for the VHDL coding effort for most of this chip. Although they joined the project late, both made significant contributions to the design as well as the implementation. In particular, I would like to acknowledge Rex for the paragonal memory layout used in the cell store, and for significant innovation in getting the pacing algorithm committed to silicon. I gave Rex many sleepless nights by insisting on a very clean design, and continually adding and removing features. He seldom complained, and always maintained good humor, which made the gruelling task bearable. I also acknowdge Will for his contributions in coding the chips internal clock domain, and the UTOPIA ports. He has left his mark on the chip in the form of an intelligent flow control algorithm which allows the chip to exert flow control signals over optical links.

I owe a lot to John DeHart in this undertaking; he was instrumental in getting the APIC device driver debugged and in a shape in which it could be distributed to Gigabit Kits participants. I admire his abilities and am grateful for his assistance in a very difficult situation, which arose when he had to undertake working with the APIC when all of the chip's developers, myself included, had left the University.

My thanks also go to Dr. Dave Richards, who spent considerable time and effort on implementing and debugging the MBus and PCI prototype cards, and on the UTOPIA port implementation. He also contributed his considerable expertise in tracking down and fixing APIC physical level problems once the chips were back from the foundry. His constant speculations about the schedule of the project were, I am sorry to say, right on mark.

I would also like to thank Margaret Flucke for undertaking the massive layout task for the chip, and Tom Chaney and Fred Rosenberger for spending long hours poring over a printout of the chip's layout to ensure signal integrity and dealing with power and clock distribution issues.

I would like to thank Dr. Jon Turner, who contributed to the project with many very useful comments and suggestions throughout the period of the project. The new and improved pacing algorithm described in Chapter 3 is due to him.

I would like to thank Andy Fingerhut, Anshul Kantawala, and Chuck Cranor for their support and help in software related issues.

I would like to thank everyone at Growth Networks, and in particular Dan Lenoski, for agreeing to let me take time off from work to finish my thesis.

Last, but not the least, I would like to thank all my friends at CCRC and ARL, whose companionship added the necessary ingredients of fun and liveliness without which life has no meaning: Ana, Anshul, Anurag, Apostolos, Brad, Cheenu, Christos, Chuck, Dan, Daphne, Diana, Girish, Gopal, Geppo, Hari, Manamohan, Marcel, Maurizio, Milind, Mini, Nimi, Paula, Penny, Samphel, Sherlia, Shree, and Vykky.

# Chapter 1 Introduction

Although gigabit network design has seen major advances in the last decade, the ability of end applications to fully exploit the capacity of these networks has been severely limited. From a throughput standpoint, there is usually a gross disparity between raw network bandwidths and the maximum effective throughput that can be achieved by end-applications. This becomes a very important issue in light of the emergence of several high bandwidth multimedia applications. In terms of latency, the networking subsystem in an end host often adds enough to the end-to-end latency that it often exceeds (or can even be several times) the network propagation and queueing delay. This is especially true in local area networks, where latency is a criticial measure of performance for interactive and distributed computing applications.

The bottlenecks in an end-host that prevent applications from exploiting all or most of the available network capacity manifest themselves in both the hardware and software realms. From a hardware perspective, limitations have traditionally been imposed by the peak system memory and bus bandwidths, and from poor network interface design practices. From a software viewpoint, the overhead of operations such as data copying, checksumming, servicing of interrupts, and context switching are typically responsible for poor performance. Several researchers have recognized the source of these bottlenecks, and identified mechanisms that are at least partially effective in overcoming some of the handicaps. This is evidenced by the considerable litearature that has been published in recent years on network interface design, and on the structuring of protocols in operating systems [2,5,6,7,10,12,14,28,32,39,41]. We have attempted to integrate a number of these "proven" good mechanisms, along with some new ones of our own creation, in our attempt to build a state-of-the-art high performance network interface. This document describes the design and implementation of this network interface chip (NIC), which is called the APIC (ATM Port Interconnect Controller).

### 1.1. Goals

The research presented in this document attempts to answer the following fundamental questions:

- Given current chip technology, is it possible to build an inexpensive network interface that can deliver all or most of the network capacity of a gigabit network to end applications? Can this be done in a way that assures some degree of quality of service (QoS) to these applications?

- Can this same network interface also efficiently support latency sensitive applications that have to coexist with high bandwidth applications?

One of the non-goals of this research is the preservation of the protocol stack software architecture currently used in most commodity operating systems. In other words, we assumed that we had the freedom to change this software architecture in order to best achieve our goal of higher performance.

While this thesis formulates several new mechanisms, not all of them have been validated through experimentation. The reason for this was to limit the scope of the work — design and implementation of a network interface chip is a complex task requiring many man-years of effort, and validation of all of the chip's features would have required considerable additional investment of time in programming and testing the required software. It is hoped that most of these chip's features will be exercised by third parties using the chip, both at Washington University and elsewhere.

### **1.2.** Features of the APIC Chip

The prototype APIC design is our attempt at providing an answer to the above questions. Targeted for ATM networks, it is capable of supporting a full duplex link rate of 1.2 Gb/s. Since one of our goals was to keep (a production version of) the NIC inexpensive, the design is geared towards implementation on a single application-specific integrated circuit (ASIC), with no external memory required for buffering or table handling. Some of the salient features of the APIC design include:

- The ability to act as a building block for System-Area Networks (SAN) and Desk-Area Networks (DAN) [26,27].

- Remote controllability.

- Multipoint and loopback support.

- DMA modes that are designed to reduce the number of data copies to zero (a zero copy architecture).

- Protected DMA and Protected I/O, which are novel techniques that allow buffer management and chip control operations to reside in user-level processes, without compromising OS protection mechanisms.

- Efficient mechanisms designed to reduce interrupt frequency and interrupt service overhead, while retaining the ability to be able to react quickly to latency sensitive events.

- Support for multiple traffic classes for QoS.

The APIC has been coded in VHDL, and passed a detailed co-verification with a C++ simulation of the chip's behavioral model. It has been successfully implemented in 0.35 micron technology, and is currently in use in several research projects at Washington University, as well as at several other universities and research labs that are part of the NSF-sponsored gigabit kits initiative. The software drivers for the chip have been implemented in the NetBSD operating system kernel, and are currently in the process of being ported to Linux.

## **1.3.** Contributions

The primary contributions of this research are:

- Design of a single chip high performance gigabit ATM host network interface with dual ATM ports, that can function both in a standalone environment as well as with other identical chips in a desk-area network environment.

- **Protected DMA and Protected I/O**: A unique meld of hardware and software that enables user-space protocols and applications to efficiently interface directly to the NIC for data movement, without any OS kernel involvement, and without compromising OS security mechanisms.

- Interrupt Demultiplexing: A feature that would permit high bandwidth and low latency applications to coexist without the adverse interactions that are common in today's implementations. Additionally, this feature can help reduce the effects of interrupt receive livelock, which is a problem that plagues almost all high performance network interfaces in use today. Taken together with user-space protocol implementations using Protected DMA and Protected I/O, interrupt demultiplexing can entirely eliminate the receive livelock problem.

- d-Heap Pacing: In order to support QoS guarantees to individual multimedia streams, the APIC supports paced connections. Compared to traditional network interfaces, the APIC can support independent pacing for very large numbers of connections; this has been made possible through a novel architecture based on hardware implementation of d-heaps.

The thesis formulates the above mechanisms and explains why we believe they will function as described. However, as mentioned earlier, we have chosen not to experimentally validate all of these mechanisms in order to limit the scope of the work; it is hoped that the many users of the chip will invest the time to write the necessary drivers to program those features not exercised by the default driver, and publish results validating many of these mechanisms.

While the APIC targets ATM as a network technology, it is important to note that many of the contributions made in this thesis are applicable in the Internet context too. In particular, it is feasible to implement Ethernet adapters that make use of many of the same techniques, provided the adapter contains a programmable packet classification engine that can classify packets based on Internet port numbers; in that case, an Internet flow would take the place of an ATM connection.

## 1.4. Outline

The rest of the thesis is organzied as follows: Chapter 2 provides background and motivation for the problem addressed herein. Related research in the area of gigabit network interfaces and desk-area networks is covered in Chapter 3. Chapter 4 lists the main contributions made in this thesis, with reference to the related work presented in Chapter 3. Chapter 5 describes the APIC architecture, while Chapter 6 lays out the chip's internal design. Chapter 7 presents a software architecture and describes implemented pieces of this architecture. Chapter 8 presents results from several experiments performed on a working prototype of the chip. Finally, Chapter 9 concludes with a summary of the contributions and ideas for future research.

# **Chapter 2**

# **Background and Motivation**

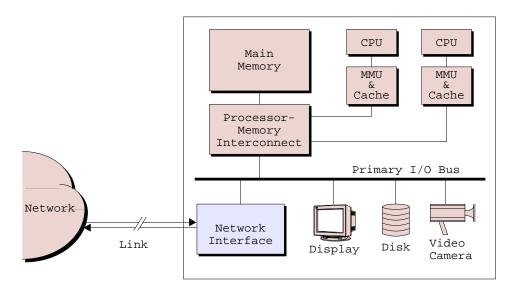

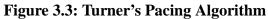

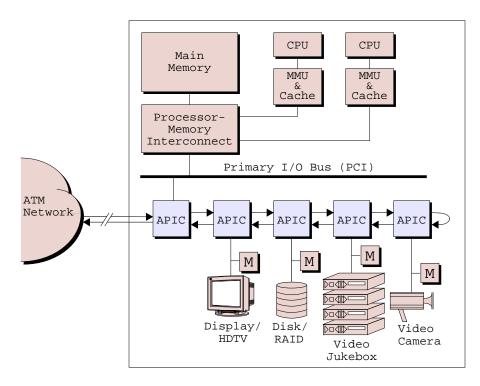

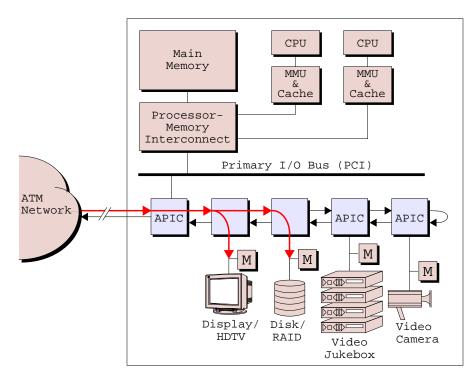

Figure 2.1 shows the typical architecture of a modern workstation or server. There are one or more processor modules which interface to the system's main memory and to a primary I/O bus via a processor-memory interconnect. The latter could be implemented as a bus, but in modern machines, it is usually a general switch chipset with internal buffering. A processor module consists of a processor, some cache, and a memory management unit (MMU) which usually contains a translation lookaside buffer (TLB). Most I/O devices interface to the primary I/O bus, either directly or through a secondary I/O bus which in turn is connected to the primary I/O bus using a bus adapter. In the figure, we do not show these secondary I/O buses, because for the most part we are interested in high bandwidth devices, including network interfaces, which interface directly to the primary I/O bus, which originated as a standard for PCs, but has subsequently gained widespread acceptance in the server and workstation markets too.

There are a few important points to note about this architecture in the context of high performance network interfacing. There are two mechanisms by which devices on the I/O bus can communicate with software running on the host processor(s). In the first technique, the software can use processor instructions to read or write data directly from or to the device. This mechanism, called "Programmed I/O", works by requiring the device to make some of its internal memory and registers available to the host processor; usually, this is achieved by mapping the device into an unused portion of the same address space that is used by the processor to access main memory. In other words, by issuing load and store instructions with these special addresses, the processor can

**Figure 2.1: Typical Host Architecture**

read or write to the registers (or memory) resident on the device. This kind of access method is also commonly referred to as "Memory-mapped I/O".

The second method used to communicate information between an I/O device and software running on the host processor is called DMA (Direct Memory Access). Here, all communication passes through special "shared" data structures that are allocated in the system's main memory. What makes these structures shared is the fact that they can be read from or written to by both the processor and the device.

In practice, both methods are used in most devices. Programmed I/O provides a synchronous access interface to the device, while DMA provides an asynchronous interface. Usually, DMA is the preferred technique when large amounts of data are to be transferred to or from memory, because it does not tie up the processor for the duration of the transfer. Programmed I/O is useful when small amounts of data are to be transferred, or when the interaction needs to be synchronous. Usually, control interactions with the device are implemented using programmed I/O.

### 2.1. DMA Subsystems

Most modern NICs use DMA as the preferred technique for moving packets to or from main memory. The DMA subsystem is the part of the NIC that is responsible for all DMA related actions. One of the required features of the DMA subsystem in a NIC is "scatter-gather DMA". This refers to the ability to be able to handle packets which are fragmented in memory. Such fragmentation occurs because packets are constructed by network protocols so that they usually reside in different regions of the memory. Additionally, a single packet may be broken up into smaller pieces that reside in different memory locations. This happens, for example, if the protocol which constructed the packet used separate buffers for the packet header and packet data.

### 2.1.1. Why is the DMA Subsystem so important?

The design of the DMA subsystem in a NIC is made complicated by the fact that there are several trade-offs to consider. One of these has to do with choosing between better memory utilization and improved performance. Another, which is more of a software issue but has a major impact on the DMA subsystem, has to do with the selection of an appropriate API (application programming interface) for applications: usually, APIs that are more convenient and easier to use result in worse performance. A poorly designed DMA subsystem which does not take into account these trade-offs and software interactions can result in phenomenally bad overall performance.

One of the most important issues to consider in the design of a DMA subsystem is the number of "data touch" operations. Any time that packet data is read from or written to main memory, it is considered to have been "touched". A design should try to minimize data touches, because of the large negative impact that they can have on performance. The reason for this is that main memory bandwidth has not kept pace with increases in processor performance, so that any reduction in the number of times memory is accessed for a given piece of data can result in large performance gains. To see this, consider the fact that the main memory bandwidth of a typical PC with a 64-bit memory bus is about 2.2 Gb/s for reads and 1.4 Gb/s for writes (these are numbers from a PIII/450MHz PC). For simplicity of analysis, let us assume that the memory bandwidth is 1.8 Gb/s for both reads and writes. If there were k data touch operations, then each word of data from the network is effectively accessed k times, which means that from the viewpoint of the consumer of the data, the effective maximum throughput that can be achieved is only (1.8/k) Gb/s. For two data touches, this number goes down to 900 Mb/s, for three to 600 Mb/s, and so on. Given the very high raw bandwidths supported by our target network (1.2 Gb/s for the APIC), it is easy to see that for anything more than a single data touch, we may not be able to exploit all of the network's capacity. And with each

Figure 2.2: Data Touch Overhead in a Typical Protocol Stack

additional data touch, the achievable throughput drops rapidly. Clearly, it is beneficial to keep the number of data touch operations to a bare minimum.

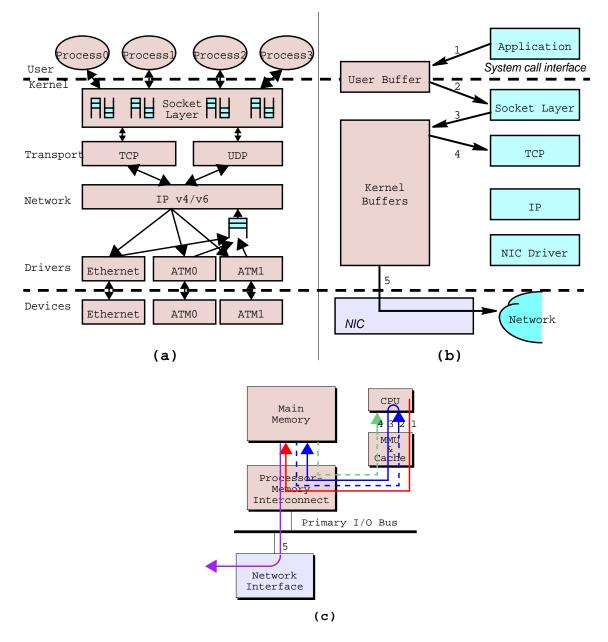

It is not unrealistic to see numbers as high as five data touches; in fact, many modern TCP/IP protocol stacks incur at least that many data touches. To see why this is so, consider Figure 2.2. Part (a) of the figure shows the traditional protocol stack architecture used in most of today's

operating systems (the example shown is for BSD Unix). Part (b) of the same figure shows what happens when an application wants to transmit data. Following the numbered events in the figure, we have:

- 1. The application, which runs as a process in user space, first generates the data to be sent and writes it to its own private buffer in user-space, following which it makes a system call to the socket layer to transmit the data;

- **2, 3.** The socket layer copies the data from the user buffer into a set of kernel buffers that are used to hold packets.

- **4.** TCP reads the data so that it can compute the checksum which has to be inserted in the packet header.

- 5. The network interface reads the data from the kernel buffer and transmits it.

Figure 2.2(c) shows what happens in hardware for these five data touch operations. Arrows represent movement of data corresponding to the five data touch operations. Notice that some of the lines are dashed; a dashed line represents the fact that the data movement indicated by the line may not actually occur if the corresponding data is in cache. For example, if the system call to transmit a packet is made soon after the application has generated or otherwise accessed the data, then the read portion of the copy ("2") from user to kernel buffer would with high likelihood be satisfied from cache. Similarly, if TCP decides to transmit the data immediately or shortly after the system call to send it is issued, then the checksum computation step "4" would be satisfied from cache. Thus, in the best case there are three data touches (to memory) for any given piece of data; in the worst case, there are five.

Using our earlier example, with 1.8 Gb/s of memory bandwidth, with five data touches we would be able to achieve a throughput of only (1.8/5) Gb/s, or 360 Mb/s.

Figure 2.2 only showed the data touches for an outgoing packet; a similar but reversed sequence applies on the incoming side.

Data touches are not bad just for throughput performance; they also adversely affect packet latency, because of the extra time the processor spends copying data. Clearly, it is important to be able to minimize data touch operations.

### 2.1.2. NIC design choices that affect the DMA Subsystem

In this section, we look at some architectural choices available to NIC designers, and how they affect the DMA subsystem.

#### Cut-through vs. Store-and-forward

Network adapters fall into two main categories: cut-through, and store- and-forward. In a cutthrough adapter, it is possible that the transmission of a frame can begin even before the entire frame has been read out of main memory. On the receiving end, a cut-through adapter can store part of a frame in main memory before the entire frame has been received. In a store-and-forward adapter, an entire frame needs to be read from main memory before the adapter will begin transmitting it. Also, a store-and- forward adapter will not write a frame into main memory until it has finished receiving the entire frame. Cut-through adapters have the advantage of lower delay, and of not requiring local memory on the network interface card (NIC) to store frames. They have the disadvantage that they might end up transmitting partial frames if there is an error, and of reporting receipt of partial or corrupted frames (which leaves the job of cleaning up to the software).

One of the possible techniques that can be employed to reduce the number of data touches is to move the transport layer checksum computation function into hardware on the NIC. This is easy to do on a store-and-forward NIC (the checksum can be computed while moving data between the NIC and main memory). But in cut-through adapters, it is not possible to compute and insert a checksum in the header of an outgoing packet, because the header may already have been transmitted by the time we finish computing the checksum. This means that either we would be forced to use a transport protocol with trailer checksumming, or incur the overhead of computing the checksum in software. Since the Internet transport protocols TCP and UDP both use header checksums, we have to incur the overhead of computing the checksum in software for these protocols, at least on the sending side. However, there is a trick which is often quoted (but seldom implemented) that can be used to allow the checksum computation for an outgoing packet to proceed without the overhead of a data touch. Referring to Figure 2.2, if the processor were to compute the checksum while copying data from the user buffer to the kernel buffer (steps 2 and 3), then no extra data touches would be involved. This scheme cannot easily be used on the receiving end, because the outcome of the checksum verification for an incoming packet needs to be known well before the copy from kernel

to user space takes place. So for incoming packets, the only way to avoid a data touch for checksum computation is to implement it on the NIC in hardware. Note that in this case, header checksums are not a problem, because although a cut-through adapter cannot usually verify the correctness of such a frame by itself, it can provide the computed checksum over the frame to the software and leave the job of verification of the checksum (i.e., comparing it to the value in the packet header) to the software.

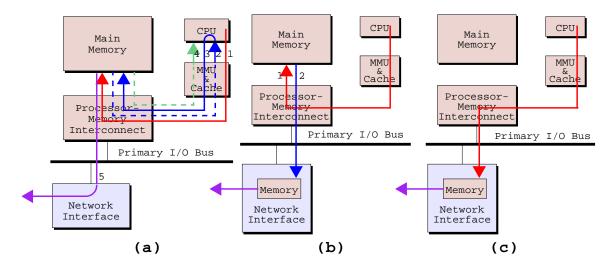

Figure 2.3: Impact of On-board Memory on Data Touches

### **On-board memory or not?**

Another design choice that affects the DMA subsystem is whether or not the NIC has an onboard memory that can be used as a staging buffer for packets. Figure 2.3 shows how the number of data touches can be reduced if a NIC contains on-board memory. Figure 2.3(a) is a repeat of Figure 2.2(c), used for comparisons. In Figure 2.3(b), the kernel buffers (see Figure 2.2(a,b)) are allocated from memory on the NIC, and the kernel moves data from user buffers into these on-board buffers using either programmed I/O or DMA. If programmed I/O is used, the checksum can be computed during the copy loop, thereby resulting in only two data touch operations (as shown in the figure). If DMA is used to move data between main memory and the network interface, then the additional data touch for checksumming can still be avoided if the network interface computes the checksum while performing the DMA operation. Figure 2.3(c) shows a third alternative which involves no main memory accesses at all (zero data touches): the user buffers are allocated from the NIC's on-board memory (we assume on-board checksum support). Although this sounds very attractive, it is usually not a very practical approach because it would require large amounts of memory on the NIC, and the application would have to know in advance where it should write its data to (i.e., to which NIC's buffer).

What if we didn't have on-board memory? As mentioned earlier, the APIC does not have any on-board memory to keep cost down. What we would like to see happen is for the data to move directly from the application's user-space buffer to the network interface, which can then directly transmit the data. Similarly, on receive, we would like to be able to receive data directly into the user buffer. As we shall see later, the APIC's Protected DMA and Protected I/O features do enable this kind of data movement.

#### **On-board processor or not?**

A number of NICs have on-board processors and firmware that is used to perform various NIC related tasks. This has both advantages and drawbacks; often, on-board processors drive up the cost of the NIC, but they provide more flexibility in the sense that more features can be added as necessary without a lot of work. Usually with such NICs, the method by which the driver for the NIC interfaces to the rest of the OS remains the same; however, some researchers have argued for moving portions of the protocol stack onto the NIC. Increasingly, this approach has gained disfavor because it requires very close interaction between the OS on the host and the software running on the NIC's processor.

### 2.2. Architectural Impact on Latency

So far, we have been focusing on the overhead of data touch operations resulting from data copying and checksumming in the protocol stack. Since data touches reduce the effective available memory bandwidth, they have an adverse effect on throughput. However, because of the extra time involved in copying and checksumming, they also affect end-to-end latency. The relative impact of these operations on latency is quite small however, except in a local-area network (LAN) where the network propagation delay can be of the order of a few tens of microseconds. Several distributed computing applications, such as distributed interactive simulations, Network File Service (NFS), remote procedure call (RPC), etc. could benefit from a very low end-to-end latency. For such latency sensitive applications, it makes sense to not only minimize the impact of data touch

operations, but also operations such as system calls, interrupts, and context switching, all of which have an adverse impact on latency. In modern operating systems, system calls and interrupt overheads can be of the order of a few to several tens of microseconds, which is comparable to the network delay in a LAN. As we shall see later, Protected DMA and Protected I/O achieve the goal of direct movement of data to and from user space without kernel involvement, thereby eliminating system call latency. That leaves the overhead of interrupts. Usually, interrupt overhead cannot be avoided for latency critical applications unless the device is continuously polled. The latter is not a practical alternative, so the cost of fielding an interrupt corresponding to a latency sensitive event, such as packet arrival, cannot be avoided.

### **2.2.1. Impact of interrupts on latency**

Interrupts pose another problem for latency sensitive applications, which manifests itself in the presence of other high bandwidth applications with which it may have to coexist. High bandwidth applications typically have a high packet arrival rate, and therefore may get interrupted very often. To reduce the processor overhead of having to service interrupts very frequently, several approaches have been suggested, all of which try to reduce the frequency of interrupts by processing multiple interrupt events with only a single interrupt. In a mixed environment with both latency-critical and high-bandwidth applications, this can have the negative side-effect of significantly increasing the latency seen by delay-sensitive applications. This is because these applications do not get timely notification of packet arrival events, since these events get processed infrequently, and in batches along with large numbers of other events corresponding to other high bandwidth applications. In such mixed environments, it would be beneficial to have some way to allow latency-critical applications to still have their interrupts serviced in a timely manner, without adversely impacting high-bandwidth applications (which are usually *not* latency-sensitive). As we will see later, the APIC's interrupt demultiplexing technique achieves this objective.

### 2.3. Receive Livelock

In an interrupt driven system, interrupt service takes priority over all other activity. As mentioned earlier, if packets arrive too fast, the system will spend all of its time processing receiver interrupts. It will therefore have no resources left to support delivery of the arriving packets to applications, and no resources to allow the application to consume the received data. The useful

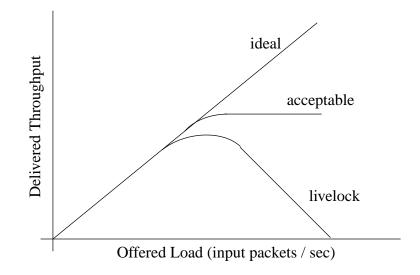

**Figure 2.4: Illustration of Receive Livelock**

throughput of the system will drop to zero. This condition is referred to as *receive livelock* [38]: a state of the system where no useful progress is being made, because the processor is entirely consumed with processing receiver interrupts.

Figure 2.4 (adapted from [38]) demonstrates the possible behavior of throughput as a function of offered input load. Ideally, no matter what the packet arrival rate, every incoming packet is processed. However, all practical systems have finite capacity, and cannot receive and process packets beyond a maximum rate (determined by the processor speed and the applicatiuon-dependent cost of receiving and processing a packet). Given this practical constraint, we would like the packet packet processing rate to remain pegged at this maximum, even when the rate of arrival of packets is higher than the maximum. However, because of the receive livelock effect, the system throughput may drop off to zero as the packet arrival rate increases, as shown in the figure. Note that this is a direct result of the fact that interrupt service takes priority over packet processing.

Related to the problem of receive livelock is the problem of starvation of transmits under overload. In most systems, packet transmission is done at a lower priority than packet reception, on the assumption that this will cause lower packet loss. However, under heavy receive traffic conditions, the system may spend most of its time servicing interrupts for incoming packets, so that packets waiting to be transmitted will not get an opportunity for service. This is called transmit starvation [38].

All proposed techniques to alleviate livelock rely on somehow matching the interrupt rate to the rate of consumption of packets, but the problem remains one that dogs all modern adapters. We propose a software technique that can delay the onset of receive livelock, thereby allowing for higher throughput before the onset of livelock. In the context of the APIC, we will also show that by combining Protected DMA and Protected I/O with Interrupt Demultiplexing, we can completely eliminate the problem of receive livelock.

### 2.4. QoS Support in Network Interfaces

Most conventional network interfaces, barring ATM interfaces, have usually not included any special support for provisioning quality of service (QoS) for different applications. In other words, they have treated all traffic in a best-effort manner. In the case of ATM networks however, the network attempts to provision different grades of service to different applications. It accomplishes this by requiring applications to contract with the network on how much traffic load they would like the network to carry. The application for its part has to ensure that it keeps to its portion of the contract, which usually means some constraints need to be imposed on the rate at which traffic is injected into the network by the application. Such constraints can be implemented in software on the end-stations, but this can provide only a very coarse-grained level of control on the traffic bursts that are fed into the network. By incorporating special QoS support on a network interface, it is possible to offload the packet scheduling work from the processor, and also to achieve much finer grain control over the profile of injected traffic. ATM network interfaces typically provide this level of QoS support in the form of *paced channels*. Each application flow is mapped into a paced channel, and the network interface ensures that all traffic from the channel is injected into the network at a pre-configured *pacing rate*.

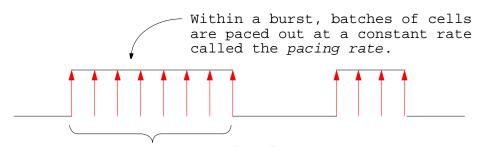

In a sense, the pacing rate is the "peak rate" for an application. However, this should not be taken to mean that only constant bit-rate (CBR) applications are supported by this paradigm: Figure 2.5 shows that a variable bit-rate (VBR) application can enqueue bursts of data (for example, video frames) that are to be transmitted on a paced channel with a fixed pacing rate. Each individual burst will be transmitted at the pacing rate, but when the network interface runs out of data

Burst scheduled by application

#### Figure 2.5: Behavior of a paced channel

to transmit at the end of a burst, no more data will be injected into the network until the next burst is enqueued for transmission by the application software. Since there are idle periods between bursts, the resulting traffic profile fits the description of a VBR stream.

How should the pacing rate for a channel be chosen? If the channel is the source of data for a switched VC (SVC) that was setup using some sort of ATM signalling mechanism, then the quality-of-service (QoS) parameters negotiated with the network during the connection setup phase will usually place an upper bound on the maximum rate at which cells on that connection can enter the network. This "peak rate" becomes the pacing rate for the connection, and it is up to the software to ensure that the traffic bursts enqueued on the channel are compliant with other negotiated QoS parameters. For a CBR source, the pacing rate should be set equal to the "constant" bit rate of the source, and the software does not need to do anything more — the APIC will take care of transmitting data from the channel at the correct rate.

What can we do if there is no contract with the network that tells us how to set the pacing rate? This happens with an ATM permanent virtual circuit (PVC), for example. One alternative is to use the network interface in best-effort mode, and rely on higher layer congestion control techniques (eg., TCP congestion control). Another alternative is to vary the pacing rate in response to feedback mechanism from the network. The feedback can be as simple as detection of a packet loss, or it can be more complex — for example, the ATM available bit-rate (ABR) mechanism uses explicit feedback from switches within the network.

Most existing ATM network interfaces do not support more than a small number of paced channels. It is assumed that the software will map multiple application flows into one of the channels. This becomes difficult to do when there are many applications with varying requirements. The reason that network interfaces have not traditionally supported larger numbers of paced channels is because the problem of hardware scheduling for many different channels with varying pacing rates is non-trivial. The APIC design incorporates a novel mechanism using hardware d-heaps to address this issue. This approach can scale to support many thousands of paced channels, and although a better solution to this problem has subsequently been proposed, the APIC's approach remains a viable, if somewhat expensive, alternative.

# 2.5. User-space Protocol Implementations

Traditionally, protocol implementations have been OS kernel-resident. In terms of throughput, this model works reasonably well if the frequency of data path operations at the user-kernel boundary is low. This is the case when an entirely kernel-resident implementation of a byte-stream transport protocol such as TCP is being used. This is because send and receive data path operations at the user-kernel boundary can work with large data buffers corresponding to application data units (ADUs), and therefore need not be very frequent. In Unix for example, these operations are implemented using read and write system calls to a socket.

If communication at the user-kernel boundary is in terms of individual packets (also called protocol data units, or PDUs), then the overhead of requiring a system call per packet can result in very poor throughput. There are two important scenarios in which this is important. The first is in the context of datagram applications, for example those using UDP. The second is in the context of user-space library implementations of protocol stacks, which are desirable for several reasons:

- They enable implementation of smaller and more efficient OS kernels (microkernels);

- User-space protocol implementations are easier to program, debug, distribute, upgrade, and maintain;

- Applications can customize protocols depending on their specific requirements;

- The process scheduling policies of the OS kernel trivially cover both application and protocol processing, which makes the task of QoS enforcement within the end-system easier.

Recently, there have been several research efforts [17,18,24,33,40] that have attempted to make user-level library implementations of protocol stacks, in such a way that they can be linked with application programs. Most of these efforts have relied on traditional network interfaces, which necessitate that the device driver be kernel-resident. Thus, even though protocols would be in user-space, transmission and reception of data would require system calls to the kernel. System calls can be expensive; a null system call can take on the order of tens of microseconds in modern workstations running derivatives of the Unix operating system. In and of itself, this is bad from the view-point of minimizing end-to-end latency for latency-senstive LAN applications. But the high cost of system calls can also result in poorer throughput if the protocols have not been implemented carefully. Most researchers who have explored library implementations of protocols have given serious attention to amortizing the overhead of a system call over multiple operations (such as send/receive of a packet) by batching them into a single system call. This places an unnecessary burden on protocol coders, and makes the code less portable and more dependent on the underlying operating system. Furthermore, it exacerbates the aforementioned latency problem.

To solve these problems, system calls and the kernel should be removed from the critical data path. In other words, the device driver for the network interface should be implementable as a library in user-space. While this can be done easily if there is only a single application process, it becomes much more difficult when there are multiple processes running on the host-processor which need to access the network simultaneously. The problem arises because conventional network interfaces are controlled by a device driver that operates in a system-wide trusted context (usually, the kernel). With multiple processes controlling the network interface directly, the issue of maintaining the operating system's protection policies between processes arises. Resolving this issue requires cooperation from the network interface in the form of special support for user-level protocols.

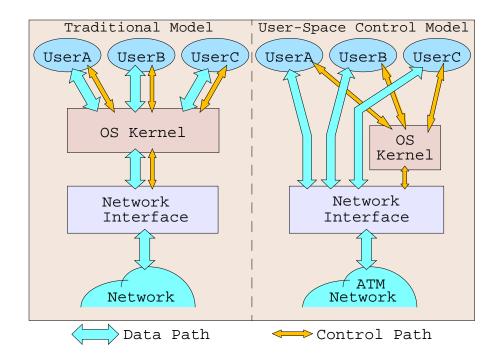

Figure 2.6 illustrates the differences between the traditional kernel-resident control model, and the user-space control model. The figure distinguishes between two kinds of control operations: those on the data path, and those on the control path. Data path operations are executed every time some data is sent or received, while control path operations are relatively rare, and usually need to be executed only once or a few times in a connection's lifetime. This distinction is important, because it means that data path operations are executed very frequently and therefore should be

Figure 2.6: Traditional versus User-space Control Model

optimized, whereas control path operations are relatively rare, so there is not much to be gained by optimizing them. Examples of data path operations include: queueing and dequeueing data buffers on queues corresponding to DMA channels, informing the network interface that there are new buffers in these queues, changing the pacing rate of a channel in response to application demands, etc. Examples of control path operations include: setting up DMA channels and connections, add-ing endpoints to a connection, etc. Note that some operations, such as setting the pacing rate, can be considered to be control path operations if they are executed only once (or rarely) as part of an initialization sequence, and can be considered to be data path operations if repeated executions are necessary every time some data has to be sent or received.

Returning to the figure, we see that in the traditional model, when a user-space process wants to use a network interface device, both control and data path operations need to pass through (and be blessed by) the OS kernel. In the user-space control model, only control path operations need to pass through (and be blessed by) the OS kernel; the frequently occuring data path operations do not need any kernel intervention (and therefore are more efficient).

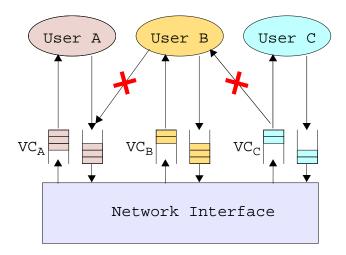

Figure 2.7: Protection concerns in the user-space control model

Since we have removed the kernel from the data path, the network interface has to take over the job of "blessing" all data path operations. Here, "blessing" means ensuring that the protection policies imposed by the kernel are not violated. In the context of an ATM network, these protection policies manifest themselves as sets of operations that are considered to be "legal" for the "owner" of an ATM connection. A user process is said to be the owner of a connection if it holds an OS granted capability for that connection. Usually, the process that is responsible for opening a connection becomes the owner of the connection. Referring to Figure 2.7, it should be illegal for user process B to send data on connection VC<sub>A</sub> which is owned by user process A. Similarly, it should be illegal for user process B to be able to receive data arriving on VC<sub>C</sub>, which is owned by user process C. As another example, one user process should not be able to change the pacing rate of a connection for which it does not hold a capability (i.e., it is not the owner). In the traditional model, such checks were performed in software by the kernel. With the user-space model, they become the responsibility of the network interface.

Note that in the context of the above discussion, a similar concept can be applied to TCP or other transport level packet flows in an IP network, in the place of ATM connections.

It is important to note that the user-space control model implies a different software structure. In particular, large portions of the network interface device driver can be migrated to user-space. We will henceforth refer to this part of the driver, which runs in an untrusted context and is typically implemented as a library that can be linked with the application, as the user-space driver. The trusted portion of the driver typically resides in the kernel, and is responsible for all control operations, for dictating protection policies that will apply to user-space drivers, and for fielding device interrupts — we will henceforth refer to this part of the driver as the kernel driver.

As we noted above, the user-space control model helps in terms of both throughput and latency. Furthermore, it enables efficient implementation of application-customizable user-space protocols. The user-space control model is a relatively new paradigm, and as we shall see, is supported by the APIC using two new mechanisms: Protected I/O and Protected DMA.

# Chapter 3

# **Related Work**

Several research groups have attempted to design and implement high-speed host-network interfaces over the past few years. The APIC design builds upon the success of these efforts by adopting a number of useful features and improving or improvising them for our target environment.

# 3.1. Related work in network interface design

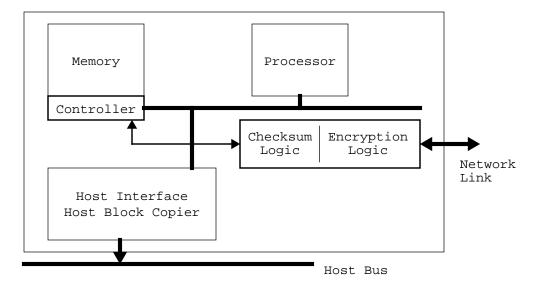

One of the earliest efforts in high-speed network interface design was the network adapter board (NAB) [32], which was especially designed to support the VMTP transport protocol [4]. As shown

Figure 3.1: Network Adapter Board (NAB) Architecture

in Figure 3.1, the board includes a microprocessor and memory subsystem. The buffer memory, which is implemented using a VRAM, is used as a staging area for the transmission and reception of packets. The serial access port of the VRAM is used for transfers between the host and the NAB, and between the NAB and the network. The random access port is used for the on-board processor to manipulate data in the memory. This processor is responsible for a lot of the "common case" packet processing, which include a firewall function and the error-free transmission of packets, while the host processor is responsible for the "rare case" processing, including acknowledgement and retransmission of packets. The main contribution of the NAB architecture was the idea of smartly partitioning protocol processing between the host CPU and the board, a concept which has seen continued use in most modern NIC designs, including the APIC.

The Nectar communications accelarator board (CAB) [1] is a host-network interface that connects through a 10 MByte/s VME interface to the host system. It too has an on-board processor, but the difference is that the CAB processor is responsible for all of the transport protocol processing. By mapping the CAB's on-board memory into the address space of the application running on the host processor, it is possible to achieve a zero-copy architecture, as was demonstrated in Figure 2.3(c). However, this style of NIC design has lost favor because of the large amounts of memory that would be required on the NIC, and because it requires close interaction between software running on the host and that on the NIC's on-board processor. Additionally, Clark et al. [5] have argued that in the case of TCP/IP the actual protocol processing is of low cost and requires very few instructions on a per-packet basis, and thus could be left on the host with minimal impact.

Washington University's Axon project [39] represents an attempt at designing a high performance host communications architecture for high-bandwidth distributed applications. This architecture allows processes to share their virtual address spaces; when a process attempts to access a segment/page that is not in its main memory, it can be retrieved from a local disk or from a remote machine. The NIC design allows network data to be copied directly into the application's address space without any store-and-forward hop, and argues that all per-packet data path protocol processing (including the transport protocol) should be implemented in hardware. As mentioned above, it has since become apparent that higher level protocol processing is best left to host software for reasons of flexibility and portability, and the impact on performance would be minimal. The Axon architecture was never implemented, but a simulation of the architecture showed promising results. ATM network interfaces bearing mention include the one from Fore Systems and Cambridge University/Olivetti Research [25], which puts minimal functionality in interface hardware. This approach assigns almost all tasks to the host processor, including segmentation and reassembly processing. This approach suffers from two drawbacks: first, modern host processor architectures are optimized for data processing, not data movement, and so the host would have to devote significant resources to manage the high-rate data movement. Second, operating system overhead of this approach can be substantial without hardware assistance for object aggregation and event management.